이번 포스트에서는 memory와 mapping 되어 있는 형태의 APB interface를 만들어보려 합니다.

1. Internal ram

○ 정의

Internal ram은 말 그대로 마이크로컨트롤러나 프로세서 내부에 존재하는 메모리입니다.

○ 사용 이유

Rate matching - 서로 다른 속도로 데이터를 처리하는 장치들 간에 데이터를 원활하게 전송하기 위해 속도 차이를 맞추는 과정

- Input (입력): 데이터를 받는 장치가 데이터를 처리하는 속도보다 더 빠르게 데이터를 전송받을 수 있기에 메모리를 사용하여 받은 데이터를 일시적으로 저장하고, 입력 장치의 속도에 맞추어 데이터를 전달하게 됩니다.

- Output (출력): 데이터를 전송하는 장치가 데이터를 받는 장치보다 더 빠르게 데이터를 처리할 수 있으며 이 때, 메모리를 사용하여 일단 데이터를 저장해 두고, 출력 장치의 속도에 맞추어 데이터를 출력하게 됩니다.

위의 이유 말고도 시스템 성능 극대화, 데이터 처리 효율성 향상, 전력 소비 감소 등의 이유로 internal ram을 사용합니다.

○ 종류

Internal ram의 종류는 다음과 같이 크게 3개로 나뉩니다.

- Single port RAM

- 말 그대로 하나의 포트만 존재하며, 읽기 또는 쓰기 작업을 한 번에 하나씩 수행할 수 있음

- Two port RAM

- 두 개의 포트가 존재하며, 동시에 접근 가능하며 두 포트가 동시에 동일한 메모리 셀에 접근할 수 있음

- Dual port RAM

- 두 개의 포트가 존재하며, 동시에 접근 가능하지만 두 포트가 동시에 동일한 메모리 셀에 접근할 수 없음

Dual, Two, Single 순으로 설계하기 어렵지만 반대로 편의성은 더 뛰어납니다.

1-2. Memory mapped single port SRAM

한 번에 하나의 읽기 또는 쓰기 작업만 수행할 수 있는 SRAM 메모리로, 이 메모리는 메모리 주소 공간에 매핑되어 CPU나 다른 장치가 주소를 통해 이 메모리에 직접 접근할 수 있는 방식으로 동작

이제부터 memory mapped single port sram을 가지고 있는 회로를 설계해보겠습니다.

이전 실습과 마찬가지로 iClk, iRsn을 사용하여 APB interface를 만들어보려 한다.

다만 이번에는 전과 달리 single port sram이 매핑되어 있는 4*32 레지스터를 만들려고 한다.

전과 같이 아래 register map에 지정되어 있는 주소에 데이터를 쓰고 읽을 것이다.

우선 읽기와 쓰기 동작을 위해서는 iCsn=0이어야 한다. 하지만 쓰기 동작을 위해서는 iWrn=0, 읽기 동작은 iWrn=1이어야 한다. 또한 APB 인터페이스를 사용할 때, 이러한 신호들이 APB에서 오는 신호에 따라 SP-SRAM 신호로 변환되어야 합니다. APB 타이밍에 따라 SP-SRAM에 쓰기 또는 읽기 작업이 수행됩니다.

Block diagram을 보면 3개의 module을 만들어야 함을 알 수 있으며 이를 Lab3_1_ApbIfBlk, Lab3_1_Top, SpSram_4x32 이렇게 3개입니다.

각 코드에 관한 설명은 주석으로 설명해 놓았습니다.

다음은 Testbench 코드입니다.

우선 3개 중 기본적인 TestBench 코드입니다.

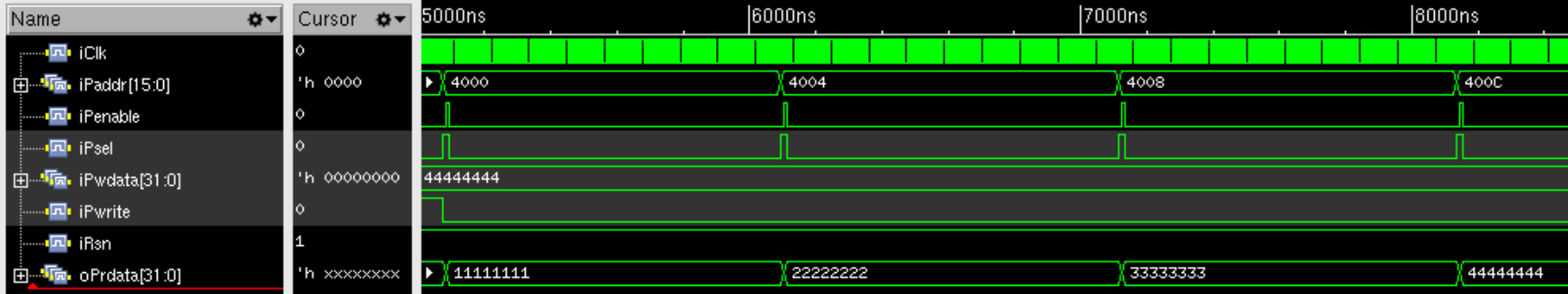

iPwrite 신호가 1이므로 iPwdata가 iPaddr에 write하는 중임을 알 수 있습니다.

iPwrite 신호가 1이므로 iPaddr에 있는 iPwdata를 read하는 중임을 알 수 있습니다.

다음은 APB 인터페이스의 동작을 task로 정의한 코드입니다

위의 코드와 동작은 달라진 점이 없으므로 시뮬레이션을 돌려도 같은 결과가 나올 것임을 알 수 있습니다.

다만, testbench 코드에서 데이터가 잘 입력되었는지 확인하는 부분이 들어갔기에 xcelium에서 display되는 것들이 달라졌음을 알 수 있습니다.

마지막 TestBench 파일은 정수 i를 설정해 0~3까지 4번 반복하는 반복문을 사용했습니다.

for (i=0 ; i<4 ; i=i+1)

begin

repeat (100) @(posedge iClk);

apb_write(16'h4000+(4*i), (i+1)*32'h11111111);

end이 부분에서 알 수 있듯이

i=0일 때 4000번지에 11111111을 저장

i=1일 때 4004번지에 22222222을 저장

i=2일 때 4008번지에 33333333을 저장

i=3일 때 400C번지에 44444444을 저장

한다는 것을 알 수 있다.

본 자료들은 혁신공유대학 차세대반도체학과 강의자료에서 발췌하였으며, 교수님의 승인 하에 사용되었습니다.

'단기강좌 - SoCs and practicing HW IP Design' 카테고리의 다른 글

| SoC 이해 및 HW IP Design (APB interface with SRAM_심화 실습) (0) | 2024.08.30 |

|---|---|

| SoC 이해 및 HW IP Design (APB interface_실습) (0) | 2024.08.17 |

| SoC 이해 및 HW IP Design (Bus interface_이론) (0) | 2024.08.17 |

| SoC 이해 및 HW IP Design (xcelium&simvision_실습) (0) | 2024.08.12 |

| SoC 이해 및 HW IP Design (SoC_이론) (0) | 2024.08.10 |