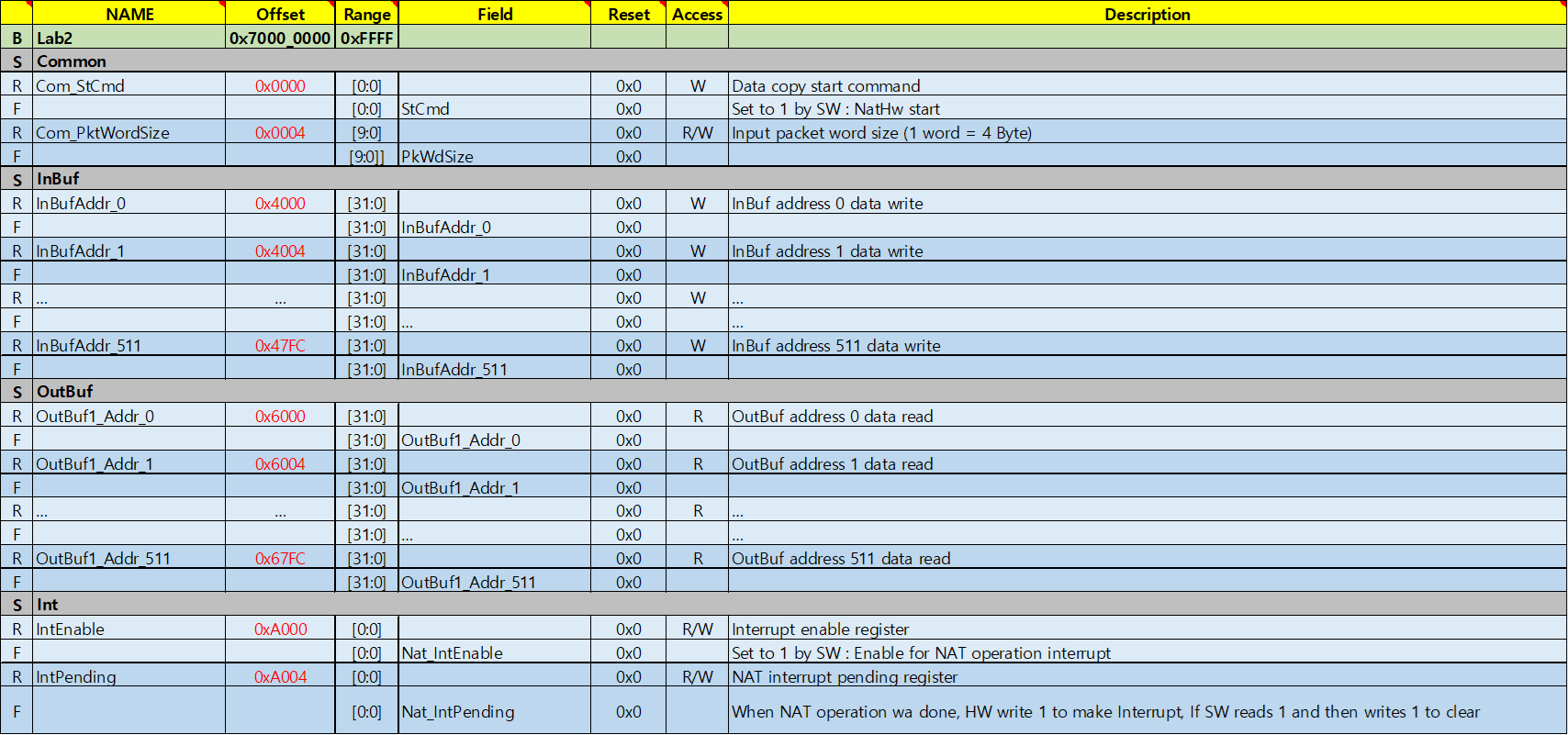

- Memory mapped register 구현

- 512 depth x 32 bit의 레지스터 배열을 구현합니다.

- APB 인터페이스를 통해 레지스터에 액세스할 수 있습니다.

- InBuf와 OutBuf의 데이터 전송

- APB 액세스를 통해 InBuf(0x4000~)에 데이터를 쓰고, InBuf에서 OutBuf로 데이터를 전송합니다.

- 이 과정에서 Endian 변환 기능을 수행합니다.

- Endian 변환 기능 : 데이터의 바이트 순서를 변경하는 기능

- 패킷 크기 설정 및 전송 시작

- Size 레지스터(0x0004)를 통해 패킷의 크기를 설정합니다.

- Start 명령(0x0000)을 사용하여 데이터 전송을 시작합니다.

- 인터럽트 생성

- 데이터 전송이 완료되면 인터럽트를 생성합니다.

- 인터럽트 활성화는 0xA000, 인터럽트 펜딩은 0xA004 레지스터를 통해 제어합니다.

- OutBuf 데이터 읽기

- APB 액세스를 통해 OutBuf(0x6000~)에서 데이터를 읽어올 수 있습니다.

위 Block diagram에서 memory mapping register의 데이터 복사 과정을 제어하기 위해 위와 같은 FSM이 사용됩니다.

- p_ldle (초기 상태)

- iStDtCp == 1'b1 조건이 참이면 p_StDtCp (데이터 캡처 시작) 상태로 전이

- p_StDtCp 상태에서 p_RdInBuf (입력 버퍼 읽기) 상태로 전이

- p_RdInBuf 상태에서 p_WrOutBuf (출력 버퍼 쓰기) 상태로 전이

- p_WrOutBuf 상태에서 else 조건으로 p_DtLatch (데이터 래치) 상태로 전이

- p_DtLatch 상태에서 p_DtCpDone (데이터 캡처 완료) 상태로 전이

- p_DtCpDone 상태에서 Next cycle로 다시 p_ldle 상태로 돌아감

InBuf에서 OutBuf로 데이터 복사가 완료되면 인터럽트 생성됩니다

- 소프트웨어에서 APB 인터페이스를 통해 IntEnable 레지스터의 0번 비트에 1을 씁니다. 이것은 인터럽트를 활성화시키는 역할을 합니다.

- 하드웨어 동작(여기서는 데이터 복사 동작)이 완료되면, wEnDtCpDone 신호가 1이 됩니다.

- wEnDtCpDone이 1이 되면, rIntPending 레지스터의 0번 비트가 1로 설정됩니다. 이것은 인터럽트가 발생했음을 나타냅니다.

- IntPending 비트가 1이 되고, IntEnable 비트도 1이면 AND gate를 통해 oInt 신호가 1이 됩니다. 이 신호는 프로세서에게 인터럽트가 발생했음을 알립니다.

- 인터럽트를 처리한 후, 소프트웨어는 다시 APB 인터페이스를 통해 IntPending 레지스터의 0번 비트에 1을 씁니다. 이는 인터럽트를 클리어하는 동작입니다.

- IntPending 비트가 클리어되면, oInt 신호도 다시 0이 됩니다.

따라서 SpSram을 감싸는 BufWrap, SpSram, Lab3_2_ApbIfBlk,Lab3_2_EndianConv, Lab3_2_Top 모듈을 만들었습니다. 위 모듈의 대한 코드는 다음과 같습니다.

512x32 비트 SRAM을 감싸는 래퍼 모듈이며 이 모듈은 SRAM의 읽기 및 쓰기 인터페이스를 관리하여, 외부 신호를 SRAM의 신호에 맞게 변환

위 코드에서

인터럽트 활성화 레지스터 (0xA000):

- 목적: 이 레지스터는 인터럽트를 활성화하거나 비활성화하는 데 사용됩니다. 인터럽트가 활성화되면, 인터럽트 신호가 발생

- 읽기 작업: 주소 0xA000에서 읽을 때, 인터럽트 활성화 레지스터 (rIntEnable)의 값이 oPrdata로 반환됩니다. 이 값은 CPU가 읽을 수 있는 데이터

- 쓰기 작업: 주소 0xA000에 쓰기를 수행하면, APB 버스의 데이터 (iPwdata[0])를 사용하여 인터럽트 활성화 플래그 (rIntEnable)를 설정 :

- iPwdata[0]이 1인 경우, 인터럽트가 활성화됩니다.

- iPwdata[0]이 0인 경우, 인터럽트가 비활성화됩니다.

인터럽트 상태 레지스터 (0xA004):

- **주소 0xA004**는 인터럽트 상태 레지스터와 관련이 있으며, 이 레지스터는 인터럽트 발생 상태를 기록합니다.

- 인터럽트 발생 상태 (rIntPending): 인터럽트가 발생했는지 여부를 저장합니다. iDtCpDone 신호가 1로 설정되면, rIntPending이 1로 설정되어 인터럽트 발생을 나타냅니다. 또한, 0xA004 주소로 쓰기를 수행하여 rIntPending을 0으로 리셋할 수 있습니다.

- 인터럽트 출력 (oInt):

- oInt 신호는 인터럽트가 활성화된 경우(rIntEnable이 1) 그리고 인터럽트가 발생한 상태인 경우(rIntPending이 1)에 1로 설정됩니다. 그렇지 않으면 0으로 설정됩니다.

이 모듈은 입력 버퍼(InBuf)에서 데이터를 읽어들여, 엔디언 변환을 적용한 후, 출력 버퍼(OutBuf)로 데이터를 전송

512x32 비트 단일 포트 SRAM의 모델링을 수행

이 모듈은 클록, 리셋, 읽기 및 쓰기 인터페이스를 통해 SRAM의 동작을 구현

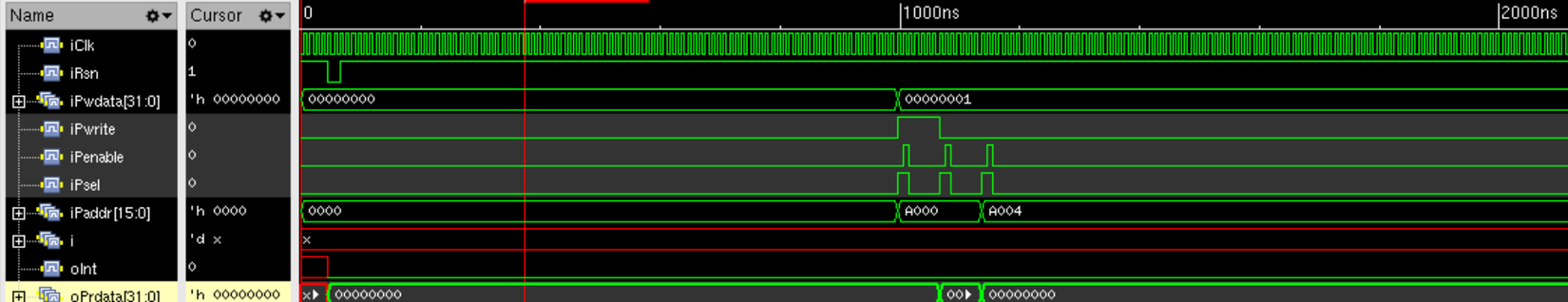

위 코드를 Simulation하기 위한 testbench 코드는 다음과 같습니다.

위의 testbench를 통해 얻어낸 xcelium 결과는 다음과 같습니다.

이 중 일부를 발췌하자면,

...

...

...

**** Write 0xffff0000 at addr 0x4000 !!! ****

**** Write 0xfefe0101 at addr 0x4004 !!! ****

**** Write 0xfdfd0202 at addr 0x4008 !!! ****

...

...

...

**** Read 0x0000ffff & expected 0x0000ffff from addr 0x6000 !!! ****

OOOO Read data Passed !!! OOOO

**** Read 0x0101fefe & expected 0x0101fefe from addr 0x6004 !!! ****

OOOO Read data Passed !!! OOOO

**** Read 0x0202fdfd & expected 0x0202fdfd from addr 0x6008 !!! ****

OOOO Read data Passed !!! OOOO

...

...

...Endian 변환기능을 통해 4000번지에 있는 InBuf의 데이터가 6000번지의 OutBuf에 거꾸로 입력되는 것을 알 수 있습니다.

본 자료들은 혁신공유대학 차세대반도체학과 강의자료에서 발췌하였으며, 교수님의 승인 하에 사용되었습니다.

'단기강좌 - SoCs and practicing HW IP Design' 카테고리의 다른 글

| SoC 이해 및 HW IP Design (APB interface with SRAM_이론 + 실습) (0) | 2024.08.30 |

|---|---|

| SoC 이해 및 HW IP Design (APB interface_실습) (0) | 2024.08.17 |

| SoC 이해 및 HW IP Design (Bus interface_이론) (0) | 2024.08.17 |

| SoC 이해 및 HW IP Design (xcelium&simvision_실습) (0) | 2024.08.12 |

| SoC 이해 및 HW IP Design (SoC_이론) (0) | 2024.08.10 |